Video Article

# A Standard and Reliable Method to Fabricate Two-Dimensional Nanoelectronics

Kristan Bryan C Simbulan<sup>1</sup>, Po-Chun Chen<sup>1,2</sup>, Yun-Yan Lin<sup>1,2</sup>, Yann-Wen Lan<sup>1,2</sup>

<sup>1</sup>Department of Physics, National Taiwan Normal University

Correspondence to: Yann-Wen Lan at ywlanblue@gmail.com

URL: https://www.jove.com/video/57885

DOI: doi:10.3791/57885

Keywords: Engineering, Issue 138, Nanoelectronics, fabrication, electron beam lithography, transition metal dichalcogenides, two-dimensional materials, standard process

Date Published: 8/28/2018

Citation: Simbulan, K.B., Chen, P.C., Lin, Y.Y., Lan, Y.W. A Standard and Reliable Method to Fabricate Two-Dimensional Nanoelectronics. J. Vis.

Exp. (138), e57885, doi:10.3791/57885 (2018).

### **Abstract**

Two-dimensional (2D) materials have attracted huge attention due to their unique properties and potential applications. Since wafer scale synthesis of 2D materials is still in nascent stages, scientists cannot fully rely on traditional semiconductor techniques for related research. Delicate processes from locating the materials to electrode definition need to be well controlled. In this article, a universal fabrication protocol required in manufacturing nanoscale electronics, such as 2D quasi-heterojunction bipolar transistors (Q-HBT), and 2D back-gated transistors are demonstrated. This protocol includes the determination of material position, electron beam lithography (EBL), metal electrode definition, et al. A step by step narrative of the fabrication procedures for these devices are also presented. Furthermore, results show that each of the fabricated devices has achieved high performance with high repeatability. This work reveals a comprehensive description of process flow for preparing 2D nano-electronics, enables the research groups to access this information, and pave the way toward future electronics.

## Video Link

The video component of this article can be found at https://www.jove.com/video/57885/

## Introduction

Since past decades, mankind has been experiencing rapid downscale in the size of transistors and, consequently, an exponential increase in the number of transistors in integrated circuits (ICs). This maintains the continuous progress of silicon-based complementary metal-oxide semiconductor (CMOS) technology<sup>1</sup>. Moreover, this current trend in the size and performance of fabricated devices are still on-track with Moore's law, which states that the number of transistors on electronic chips, as well as their performance, doubles roughly every two years<sup>2</sup>. CMOS transistors are present in most, if not all, of the electronic devices available in the market and thus making it an integral part of human lives. Due to this, there are continuous demands for improvements in chip size and performance which have been pushing the manufacturers to keep following the Moore's law track.

Unfortunately, Moore's law appears to be nearing its end due to the amount of heat generated as more silicon circuitry is squeezed into a small area<sup>2</sup>. This calls for new types of materials that can provide the same, if not better, performance as silicon and, at the same time, can be implemented in a relatively smaller scale. Recently, new promising materials have been subjects of many material science researches. Such materials as one-dimensional (1D) carbon nanotubes<sup>3,4,5,6,7</sup>, 2D graphene<sup>8,9,10,11,12</sup>, and transition metal dichalcogenides (TMDs)<sup>13,14,15,16,17,18</sup>, are good candidates that can be used as substitute for the silicon-based CMOS and continue the Moore's law track.

Fabrication of small-scale devices requires careful determination of the material's location to successfully proceed to the other fabrication techniques such as lithography and metal electrode definition. So, the method presented in this paper was designed to address this need. Compared to the traditional semiconductor fabrication techniques<sup>19</sup>, the approach presented in this paper is tailor-fitted to the development of small-scale devices which needs more attention in terms of finding the location of the material. The aim of this method is to reliably fabricate 2D nanomaterial devices, such as 2D back-gated transistors and Q-HBTs, using standard fabrication processes. This can serve as a platform for future nanodevice developments as it paves the way towards the production of future advanced nano-scale devices.

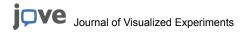

In the proceeding section, the fabrication processes for 2D materials-based devices namely, the Q-HBT and 2D back-gated transistor are discussed in detail. Electron beam patterning combined with material location determination and metal electrode definition comprises the protocol since they are required in both mentioned processes. Part 1 discusses the step-by-step fabrication process of Q-HBTs<sup>20</sup>; and part 2 demonstrates a universal approach to obtain chemical vapor deposition (CVD) molybdenum disulfide (MoS<sub>2</sub>) back-gated transistors from transfer to lift-off<sup>21</sup>, which has been completely shown in the article. The detailed process flow is illustrated in (**Figure 1**).

<sup>&</sup>lt;sup>2</sup>National Applied Research Laboratories (NARL), National Nano Device Laboratories (NDL)

## **Protocol**

# 1. 2D Quasi-heterojunction Transistors Fabrication Process

- 1. Prepare commercial c-plane sapphire.

- 1. Wash the whole single-side polished sapphire (2-inch) with acetone.

- 2. Rinse the sapphire substrate with isopropyl alcohol.

- 2. Grow MoS<sub>2</sub> on sapphire substrate using CVD in a hot-wall furnace.

- 1. Place 0.6 g of molybdenum trioxide (MoO<sub>3</sub>) powder in a quartz boat located at the heating zone center of the furnace. Put the sapphire substrate downstream next to the quartz boat containing the MoO<sub>3</sub> powder.

- 2. Prepare sulfur (S) powder in a separate quartz boat at the upstream side of the furnace. Maintain its temperature at 190 °C during the reaction.

- 3. Use argon (Ar = 70 sccm, 40 Torr) gas flow to bring the S and  $MoO_3$  vapors to the sapphire substrate while heating the center zone to 750 °C.

- 4. Keep the heating zone, after reaching the desired growth temperature of 750 °C, for 15 min and then naturally cool down the furnace to room temperature.

#### Perform EBL.

NOTE: A thin Au of about 5 nm was deposited by the sputtering for discharging during all EBL processes on sapphire substrate

- 1. Identify, using an optical microscope, an area where MoS<sub>2</sub> monolayer flakes are observed, then design the stripe pattern layout for that specific area using a design software (AutoCAD).

- 2. Spin-coat photoresist (PR), for example polymethyl methacrylate (PMMA) or P015, on top of the sample at 2000 rpm for 60 s (room temperature). Ensure that the PR has covered the entire sample after spin coating.

- 3. Heat the sample (Soft Bake) at 100 °C for 90 s in order to evaporate the solvents in the PR and enhance the adhesion.

- 4. Convert the pattern layout in step 1.3.1 into a specific file (example: GDS file), and upload it in the EBL software.

- Determine the ideal dose of electron beam based on the width of the lines in the layout.

NOTE: For line width narrower than 1 μm, the ideal dose of electron beam is 110 μC/cm<sup>2</sup>; for 1 to 5 μm line width, the dose is 100 μC/cm<sup>2</sup>; and for line width wider than 5 μm, the dose is 80 μC/cm<sup>2</sup>.

- 6. Start exposing the sample to electron beam.

- Apply post-exposure bake (PEB) on the sample after the exposure in order to reduce the standing wave effects. Heat the sample at 120 °C for 90 s.

- 8. Use tetramethylammonium hydroxide (TMAH) 2.38% as developer. Immerse the sample to TMAH for 80 s. Wash out the TMAH with 200 mL of deionized water for 10 s.

- 9. Examine if the pattern is well developed by optical microscopy.

- 10. Conduct hard bake to get rid of extra water in PR. Heat the sample at 110 °C for 90 s.

- 4. Define the stripe structures using 50 W oxygen (O2) plasma etching (1st etching) for 30 s to 2 min and remove PR using 50 mL of acetone.

- 5. Grow tungsten diselenide (WSe<sub>2</sub>) using CVD on the target location, which will result in a preferred growth of WSe<sub>2</sub> layer between the already existing MoS<sub>2</sub> stripes on the sapphire substrate.

- 1. Place 0.6 g of tungsten trioxide (WO<sub>3</sub>) powder in a quartz boat located at the heating zone center of the furnace. Put the sapphire substrate downstream next to the quartz boat containing the WO<sub>3</sub> powder.

- 2. Prepare selenium (Se) powder in a separate quartz boat at the upstream side of the furnace. Maintain its temperature at 260 °C during the reaction.

- 3. Use  $Ar/H_2$  (Ar = 90 sccm,  $H_2$  = 6 sccm, 20 Torr) gas flow to bring the Se and  $WO_3$  vapors to the sapphire substrate while heating the center zone to 925 °C.

- 4. Keep the heating zone, after reaching the desired growth temperature of 925 °C, for 15 min and then naturally cool down the furnace to room temperature.

- 6. Fabricate the metal pad arrays and alignment marks.

- 1. Overlay the patterns of metal pad arrays and alignment the marks using photolithography patterning technique.

- 2. Deposit 20 nm/60 nm Ti/Au using electron gun evaporator.

- NOTE: Gold is used to avoid the oxidization of the metal pads.

- 3. Prepare and submerge the sample to 100 mL of acetone to dissolve PR and perform lift-off. Shake and blow the acetone while monitoring the whole process via optical microscopy until the metal pads become apparent.

- 7. Perform another EBL process to overlay a ribbon shape pattern on top of the MoS<sub>2</sub>-WSe<sub>2</sub> heterojunction.

- 1. Measure the coordinate displacement between the target locations in the MoS<sub>2</sub>-WSe<sub>2</sub> heterojunction and the alignment marks using optical microscopy and design the ribbon-shape layout based on these measurements using a software (AutoCAD).

- 2. Spin-coat PR, for example PMMA or P015, on top of the sample at 2000 rpm for 60 s (room temperature). Ensure that the PR has covered the entire sample after spin coating.

- 3. Heat the sample (Soft Bake) at 100 °C for 90 s in order to evaporate the solvents in the PR and enhance the adhesion.

- 4. Convert the pattern layout in step 1.7.1 into a specific file (example: GDS file), and upload it in the EBL software.

- 5. Determine the ideal dose of electron beam based on the width of the lines in the layout.

NOTE: For line width narrower than 1 μm, the ideal dose of electron beam is 110 μC/cm²; for 1 to 5 μm line width, the dose is 100 μC/cm²; and for line width wider than 5 μm, the dose is 80 μC/cm².

- 6. Set up the EBL machine such that the position of the alignment marks in the sapphire substrate matches its correspondence in the layout.

- 7. Start exposing the sample to electron beam.

- 8. Apply PEB on the sample after exposure in order to reduce the standing wave effects. Heat the sample at 120 °C for 90 s.

- 9. Use TMAH 2.38% as the developer. Immerse the sample to TMAH for 80 s. Wash out the TMAH with 200 mL deionized water for 10 s.

- 10. Examine if the pattern is well developed by optical microscopy.

- 11. Conduct hard bake to get rid of extra water in PR. Heat the sample at 110 °C for 90 s.

- 8. Use O<sub>2</sub> plasma etching (2<sup>nd</sup> etching) to define a ribbon-shaped lateral heterojunction, and remove PR by acetone.

- 9. Perform the EBL process to overlay the pattern of the Ti/Au metal electrodes.

- Measure the coordinate displacement between the target locations in the MoS<sub>2</sub>-WSe<sub>2</sub> heterojunction and the alignment marks using optical microscopy and design the metal electrode layout based on these measurements using a software (AutoCAD).

- 2. Spin-coat PR, for example PMMA or P015, on top of the sample at 2000 rpm for 60 s (room temperature). Ensure that the PR has covered the entire sample after spin coating.

- 3. Heat the sample (Soft Bake) at 100 °C for 90 s in order to evaporate the solvents in the PR and enhance the adhesion.

- 4. Convert the pattern layout in step 1.9.1 into a specific file (example: GDS file), and upload it in the EBL software.

- Determine the ideal dose of electron beam based on the width of the metal lines in the layout.

NOTE: For metal line width narrower than 1 μm, the ideal dose of electron beam is 110 μC/cm²; for 1 to 5 μm line width, the dose is 100 μC/cm²; and for line width wider than 5 μm, the dose is 80 μC/cm².

- 6. Set up the EBL machine such that the positions of the alignment marks in the sapphire substrate matches its correspondence in the layout.

- 7. Start exposing the sample to electron beam.

- 8. Apply PEB on the sample after exposure in order to reduce the standing wave effects. Heat the sample at 120 °C for 90 s.

- 9. Use TMAH 2.38% as the developer. Immerse the sample to TMAH for 80 s. Wash out the TMAH with 200 mL deionized water for 10 s.

- 10. Examine if the pattern is well developed by optical microscopy.

- 11. Conduct hard bake to get rid of extra water in PR. Heat the sample at 110 °C for 90 s.

- 10. Perform Ti/Au Metal Deposition and Lift-off

- 1. Deposit Ti/Au metal using electron gun evaporator with the thickness of less than 100 nm, otherwise, it will be difficult to remove the PR and the unwanted metal by lift-off.

- 2. Prepare and submerge the sample to 100 mL of acetone to dissolve PR and perform lift-off. Shake and blow the acetone while monitoring the whole process via optical microscopy until there are only metal lines and pads left.

- 11. Perform the EBL process in step 1.9 but overlay the Pd/Au metal electrode's pattern instead of Ti/Au.

- 12. Perform the metal deposition and lift-off process in step 1.10 but deposit Pd/Au instead of Ti/Au.

# 2. 2D Back-gated Transistors Fabrication Process

- 1. Prepare back-gated Si/SiO<sub>2</sub> substrates with alignment marks.

- 1. Prepare homemade or commercial SiO<sub>2</sub>/Si substrate.

- 2. Use photolithography or EBL patterning techniques to define the alignment mark.

- 3. Perform reactive ion etching (RIE) on the SiO<sub>2</sub>/Si substrate until the total depth of the target area reaches 1000 nm and remove the PR by O<sub>2</sub> plasma to reveal the formed alignment marks.

- 4. Overlay the patterns of metal pad arrays using photolithography patterning technique.

- 5. Deposit 20 nm/60 nm Ti/Au using electron gun evaporator.

- NOTE: Gold is used to avoid oxidization of the metal pads.

- 6. Prepare and submerge the sample to 100 mL of acetone to dissolve PR and perform lift-off. Shake and blow the acetone while monitoring the whole process by optical microscopy until the metal pads become apparent.

- 2. Perform CVD of MoS<sub>2</sub> on sapphire substrate in a hot-wall furnace.

- 1. Place 0.6 g of MoO<sub>3</sub> powder in a quartz boat located at the heating zone center of the furnace. Put the sapphire substrate downstream next to the quartz boat containing the MoO<sub>3</sub> powder.

- 2. Prepare S powder in a separate quartz boat at the upstream side of the furnace. Maintain its temperature at 190 °C during the reaction.

- 3. Use argon (Ar = 70 sccm, 40 Torr) gas flow to bring the S and MoO<sub>3</sub> vapors to the sapphire substrate while heating the center zone to 750 °C.

- 4. Keep the heating zone, after reaching the desired growth temperature of 750 °C, for 15 min and then naturally cool down the furnace to room temperature.

- 3. Transfer MoS<sub>2</sub> from the sapphire to the back-gated SiO<sub>2</sub>/Si substrate.

- 1. Spin coat PMMA with the spin speed of 3500 rpm for 30 s on top of the MoS<sub>2</sub> film.

- 2. Bake the MoS<sub>2</sub>/sapphire sample at 120 °C for 3 min in order to strengthen the PMMA coating.

- 3. Dip the MoS<sub>2</sub>/Sapphire sample into 50 mL of ammonia solution (14.5%) for around 30 min to 2 h to separate the MoS<sub>2</sub> film from the sapphire substrate.

- 4. Pick up the film and transfer it to the SiO<sub>2</sub>/Si substrate.

- 5. Bake the MoS<sub>2</sub>/SiO<sub>2</sub>/Si sample in order to enhance the adhesion between the MoS<sub>2</sub> and SiO<sub>2</sub> layers. Heat the sample at 120 °C for around 30 min to 1 h.

- 6. Remove the PMMA by washing it with 30 mL of acetone for around 30 min to 2 h.

- 7. Rinse the sample with isopropyl alcohol and use nitrogen to blow it dry.

- 4. Perform EBL.

NOTE: There is no thin Au deposited on SiO<sub>2</sub>/Si substrate during EBL process since Si is somehow conductive.

- Measure the coordinate displacement between the target locations and the alignment marks using optical microscopy and, based on these measurements, design the pattern layout of the metal electrodes using a design software.

NOTE: Metal electrodes connect the target points in the MoS<sub>2</sub> sample to the metal pads in the SiO<sub>2</sub>/Si substrate.

- 2. Spin-coat PR, for example PMMA or P015, on top of the sample at 2000 rpm for 60 s (room temperature). Ensure that the PR has covered the entire sample.

- 3. Heat the sample (Soft Bake) at 100 °C for 90 s in order to evaporate the solvents in the PR and enhance the adhesion.

- 4. Convert the pattern layout in step 2.4.1 into a specific file (example: GDS file), and upload it in the EBL software.

- Determine the ideal dose of electron beam based on the width of the metal lines in the layout.

NOTE: For metal line width narrower than 1 μm, the ideal dose of electron beam is 110 μC/cm²; for 1 to 5 μm line width, the dose is 100 μC/cm²; and for line width wider than 5 μm, the dose is 80 μC/cm².

- 6. Set up the EBL machine such that the position of the alignment marks in the Si/SiO<sub>2</sub> substrate matches its correspondence in the layout.

- 7. Start exposing the sample to electron beam.

- 8. Apply PEB on the sample after the exposure in order to reduce the standing wave effects. Heat the sample at 120 °C for 90 s.

- 9. Use TMAH 2.38% as the developer. Immerse the sample to TMAH for 80 s. Wash out the TMAH with 200 mL of deionized water for 10 s.

- 10. Examine if the pattern is well developed by optical microscopy.

- 11. Conduct hard bake to get rid of extra water in PR. Heat the sample at 110 °C for 90 s.

- 5. Perform Au Metal Deposition and Lift-off

- 1. Deposit Au metal using electron gun evaporator with the thickness of less than 100 nm, otherwise, it will be difficult to remove the PR and the unwanted metal by lift-off.

- 2. Prepare and submerge the sample to 100 mL of acetone to dissolve PR and perform lift-off. Shake and blow the acetone while monitoring the process via optical microscopy until there are only metal lines and pads left.

## **Representative Results**

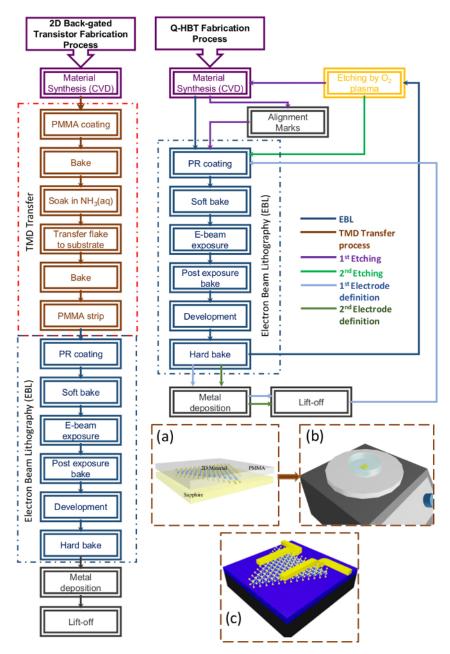

The device fabrication processes have been applied to several of the corresponding author's researches involving the development of 2D material devices. In this part, the results of some of these researches are presented to demonstrate the effectivity of the protocol discussed above. A monolayer of lateral  $WSe_2$ - $MOS_2$  Q-HBT<sup>20</sup> is selected as the first example. Using the standard device fabrication processes detailed in the protocol, the monolayer lateral  $WSe_2$ - $MOS_2$  heterojunctions were grown (**Figure 2a**) and then proceeded by the formation of the Q-HBT. Metal contacts were deposited on top of the lateral heterojunction to complete the Q-HBT. Ti/Au were deposited on top of the  $MOS_2$  layer (**Figure 2d**). Several lateral Q-HBT were developed, such as the one with an n-p-n-p lateral heterojunction illustrated in (**Figure 2d**, **2e**). The function of the Q-HBT device was verified by looking into its characteristic curves such as its output ( $I_C$ - $V_C$ ) curve at common-emitter configuration (**Figure 2f**). **Figure 2f** shows that the lateral n-p-n Q-HBT works under two operating modes - the saturation mode and the active mode - which proves that the Q-HBT that was built using the fabrication process, indeed, functions as a transistor.

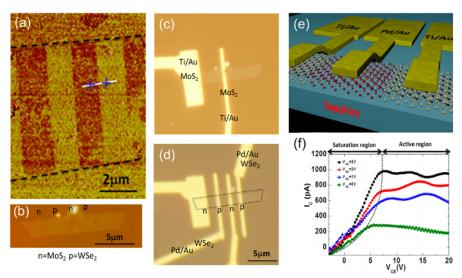

The process was also used to build 2D back-gated devices for  $MoS_2$  piezotronic strain/force sensor<sup>21</sup> application. High-quality triangular monolayer  $MoS_2$  films were first synthesized using CVD in a sapphire substrate and then transferred into a  $Si/SiO_2$  substrate. The rest of the process of making the  $MoS_2$  film into a piezotronic device is discussed in the protocol section. **Figure 3a** shows an atomic force microscopy (AFM) image of a completed device consisting of a triangular  $MoS_2$  monolayer and several sets of source/drain (S-D) Au electrodes. To study the piezoelectric polarization direction, multiple contact electrodes around the triangle shape were intentionally designed. **Figure 3b** presents the schematic diagram of the piezotronic sensor device and the setup showing how a mechanical load is applied by an AFM tip to test its piezoelectric effect. Results in **Figure 3c** show that the sensor device's current flowing through one of its S-D electrode pairs decreases for every increase in applied force and vice versa, which is an expected behavior for a piezo sensor. Furthermore, the data in **Figure 3d** implies that the developed sensor is stable since a repeating application of applied force/strain barely changed its output current or response.

Figure 1. Schematic process flow of 2D electronic devices. The blue arrows represent the fabrication process flow of Q-HBT and brown for 2D back-gated transistor. Inset: (a) the 2D material on sapphire substrate coated with PMMA; (b) a sample heated while soaked in ammonia solution; (c) schematic diagram of a 2D material after metal deposition and lift-off process. Please click here to view a larger version of this figure.

Figure 2. Two-dimensional lateral Q-HBT. (a). Phase image of AFM. The phase image shows clear contrast between WSe<sub>2</sub> and MoS<sub>2</sub>. (b). The optical micrograph of a lateral heterostructure ribbon where n-type material is MoS<sub>2</sub> and p-type material is WSe<sub>2</sub>. (c). The optical micrograph of the metal Ti/Au deposited on top of MoS<sub>2</sub> in the lateral heterostructure ribbon. Note that this image has the same scale as in (d). (d). The optical micrograph of the lateral Q-HBT, showing an n-p-n-p lateral heterojunction. Black dashed box marks the position of the lateral heterostructure ribbon. (e). Schematic plot of a 2D Q-HBT. The yellow ribbons are MoS<sub>2</sub> monolayers and the red ribbon is WSe<sub>2</sub> monolayer. Ti/Au metal layers are designed to deposit on MoS<sub>2</sub> while Pd/Au contacts with WSe<sub>2</sub>. (f). The output characteristics of the lateral n-p-n Q-HBT at different  $V_{BE}$  values. Reprinted with permission from Blaschke, B. M., et al. <sup>10</sup>. Please click here to view a larger version of this figure.

**Figure 3. The MoS**<sub>2</sub> monolayer device. (a). AFM image of the MoS<sub>2</sub> monolayer device. (b). Schematic illustration of a MoS<sub>2</sub> device showing how a mechanical load is applied by an AFM tip to test its piezoelectric effect. (c). *I-V*<sub>b</sub> characteristics of the MoS<sub>2</sub> device at different applied forces under compressive strain when applying forces at locations denoted in upper inset resulting in compressive strain as shown schematically in lower insets. (d). Current response of CVD monolayer MoS<sub>2</sub> device at repeated compressive strains at a fixed bias voltage of 1 V. Reprinted with permission from Lan, Y. W., *et al.*<sup>8</sup>. Please click here to view a larger version of this figure.

## **Discussion**

In this article, the detailed procedures of fabricating novel electronics based on 2D materials in nanometer scale are demonstrated. Since the sample preparation procedures of each application have differences with each other, the overlapped processes were treated as the protocol. Electron beam patterning combined with material location determination and metal electrode definition thus serves as the protocol here. Among the two types of devices mentioned, the whole process of 2D back-gated transistors starting at wet transferring single crystal MoS<sub>2</sub> films onto SiO<sub>2</sub>/Si substrates and ending at metal lift-off were presented. The reason why focus is given on 2D back gated transistors is the urgent need of

improved 2D materials-based field effect transistors (FETs). Therefore, important points related to its fabrication process will be emphasized in the following paragraphs.

There are some tricky points in every step of the experiments. Firstly, the precedence of material locating followed by the removal of PMMA is required to avoid unfavorable adsorption while exposing the MoS<sub>2</sub> films to air. The adsorption is one of the causes of performance degradation. Consequently, baking the sample, with a duration that is supposed to be longer than 30 min, after the transfer is necessary. Otherwise, the film is easy to be peeled off when dissolving PMMA with acetone due to the poor attachment of the films and dielectric, which results in the disappearance of the flakes at target positions. The dose of electron beam is another critical factor for patterning. High electron beam dosage is not suitable for patterns with narrow spacing between electrodes due to the proximity effect. On the other hand, decreasing its dosage may lead to the inability to achieve the ideal pattern. Fine tuning of the parameters of electron beam therefore needs to be conducted. Basically, a thin metal is preferable for easier lift-off, and its ideal thickness depends on the application and the thickness of the photo resist. For the 2D transistor in this project, metal thickness below 100 nm is acceptable.

One limitation of the method is that manual operation is required, so it is only suitable for research purposes. Once wafer scale synthesis techniques of these materials become well-developed, traditional semiconductor technology can take over this approach. Also, a trade-off between getting a higher resolution and material quality exists when choosing between optical imaging and the alternative method using scanning electron microscope (SEM) in determining the material location. The optical imaging method used in this protocol provides micrometer scale precision for locating positions, while SEM is more precise but could induce damage in the material. Therefore, using optical imaging as proposed in the protocol is the most expedient by far.

Since years of research seeking for the best way to develop new materials is indispensable, laboratory scope manufacturing with hands-on experiments still occupies an important position. Surely, this method can serve not only for 2D materials but also for 1D and the undiscovered materials in future, broadening the possibilities of nanoscale electronics.

## **Disclosures**

The authors have nothing to disclose.

## **Acknowledgements**

This work was supported by the National Science Council, Taiwan under contract No. MOST 105-2112-M-003-016-MY3. This work was also in part supported by the National Nano Device Laboratories and e-beam laboratory in electrical engineering of National Taiwan University.

#### References

- 1. Kim, Y.-B. Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics. *Transactions on Electrical and Electronic Materials*. **11** (3), 93-105 (2010).

- 2. Waldrop, M.M. The chips are down for Moore's law. Nature. 530 (7589), 144-147 (2016).

- Lan, Y.W., Chang, W. H., et al. Effects of oxygen bonding on defective semiconducting and metallic single-walled carbon nanotube bundles. Carbon. 50 (12), 4619-4627 (2012).

- 4. Lan, Y.W., Aravind, K., Wu, C. S., Kuan, C. H., Chang-Liao, K.S., & Chen, C. D. Interplay of spin-orbit coupling and Zeeman effect probed by Kondo resonance in a carbon nanotube quantum dot. *Carbon.* **50** (10), 3748-3752 (2012).

- 5. Lan, Y.W., Nguyen, L.N., Lai, S.J., Lin, M.C., Kuan, C.H., & Chen, C.D. Identification of embedded charge defects in suspended silicon nanowires using a carbon-nanotube cantilever gate. *Applied Physics Letters.* **99** (5), (2011).

- 6. De Volder, M.F.L., Tawfick, S.H., Baughman, R.H., & Hart, a J. Carbon nanotubes: present and future commercial applications. *Science (New York, N.Y.).* **339** (6119), 535-9 (2013).

- 7. Eatemadi, A., Daraee, H., et al. Carbon nanotubes: Properties, synthesis, purification, and medical applications. *Nanoscale Research Letters*. **9** (1), 1-13 (2014).

- 8. Lan, Y.W., Chang, W.H., et al. Polymer-free patterning of graphene at sub-10-nm scale by low-energy repetitive electron beam. Small. 10 (22), 4778-4784 (2014).

- 9. Romero, M.F., Bosca, A., et al. Impact of 2D-Graphene on SiN Passivated AlGaN/GaN MIS-HEMTs Under Mist Exposure. *IEEE Electron Device Letters*. **38** (10), 1441-1444 (2017).

- 10. Blaschke, B.M., Tort-Colet, N., et al. Mapping brain activity with flexible graphene micro-transistors. 2D Materials. 4 (2), 25040 (2017).

- 11. Zhu, Z., Murtaza, I., Meng, H., & Huang, W. Thin film transistors based on two dimensional graphene and graphene/semiconductor heterojunctions. *RSC Advances.* **7** (28), 17387-17397 (2017).

- 12. Kim, S.J., Choi, K., Lee, B., Kim, Y., & Hong, B.H. Materials for Flexible, Stretchable Electronics: Graphene and 2D Materials. *Annual Review of Materials Research.* **45** (1), 63-84 (2015).

- 13. Manzeli, S., Ovchinnikov, D., Pasquier, D., Yazyev, O.V., & Kis, A. 2D transition metal dichalcogenides. *Nature Reviews Materials.* 2, 17033 (2017).

- 14. Kolobov, A.V., & Tominaga, J. Emerging Applications of 2D TMDCs. Springer Series in Materials Science, 239, 473-512 (2016).

- 15. Nguyen, L.N., Lan, Y.W., et al. Resonant tunneling through discrete quantum states in stacked atomic-layered MoS2. Nano Letters. 14 (5), 2381-2386 (2014).

- 16. Torres, C.M., Lan, Y.W., et al. High-Current Gain Two-Dimensional MoS2-Base Hot-Electron Transistors. Nano Letters. 15 (12), 7905-7912 (2015).

- 17. Jariwala, D., Sangwan, V.K., Lauhon, L.J., Marks, T.J., & Hersam, M.C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. ACS Nano. 8 (2), 1102-1120 (2014).

- 18. Choi, W., Choudhary, N., Han, G.H., Park, J., Akinwande, D., & Lee, Y.H. Recent development of two-dimensional transition metal dichalcogenides and their applications. *Materials Today.* **20** (3), 116-130 (2017).

- 19. Xiao, H. *Introduction to Semiconductor Manufacturing Technology, Second Edition.* Society of Photo-Optical Instrumentation Engineers: (2012).

- 20. Lin, C. Y., Zhu, X., et al. Atomic-Monolayer Two-Dimensional Lateral Quasi-Heterojunction Bipolar Transistors with Resonant Tunneling Phenomenon. ACS Nano. 11 (11), 11015-11023 (2017).

- 21. Qi, J., Lan, Y.W., et al. Piezoelectric effect in chemical vapour deposition-grown atomic-monolayer triangular molybdenum disulfide piezotronics. *Nature Communications*. **6**, 7430 (2015).