Video Article

# Fabrication of Gate-tunable Graphene Devices for Scanning Tunneling Microscopy Studies with Coulomb Impurities

Han Sae Jung<sup>1,2</sup>, Hsin-Zon Tsai<sup>1</sup>, Dillon Wong<sup>1</sup>, Chad Germany<sup>1</sup>, Salman Kahn<sup>1</sup>, Youngkyou Kim<sup>1,3</sup>, Andrew S. Aikawa<sup>1</sup>, Dhruv K. Desai<sup>1</sup>, Griffin F. Rodgers<sup>1</sup>, Aaron J. Bradley<sup>1</sup>, Jairo Velasco Jr.<sup>1</sup>, Kenji Watanabe<sup>4</sup>, Takashi Taniguchi<sup>4</sup>, Feng Wang<sup>1,5,6</sup>, Alex Zettl<sup>1,5,6</sup>, Michael F. Crommie<sup>1,5,6</sup>

Correspondence to: Michael F. Crommie at crommie@berkeley.edu

URL: https://www.jove.com/video/52711

DOI: doi:10.3791/52711

Keywords: Engineering, Issue 101, Physics, graphene, electrostatic gating, scanning tunneling microscopy (STM), Coulomb impurity, chemical vapor deposition (CVD), poly(methyl methacrylate) (PMMA) transfer, wire bonding

Date Published: 7/24/2015

Citation: Jung, H.S., Tsai, H.Z., Wong, D., Germany, C., Kahn, S., Kim, Y., Aikawa, A.S., Desai, D.K., Rodgers, G.F., Bradley, A.J., Velasco Jr., J., Watanabe, K., Taniguchi, T., Wang, F., Zettl, A., Crommie, M.F. Fabrication of Gate-tunable Graphene Devices for Scanning Tunneling Microscopy Studies with Coulomb Impurities. *J. Vis. Exp.* (101), e52711, doi:10.3791/52711 (2015).

#### **Abstract**

Owing to its relativistic low-energy charge carriers, the interaction between graphene and various impurities leads to a wealth of new physics and degrees of freedom to control electronic devices. In particular, the behavior of graphene's charge carriers in response to potentials from charged Coulomb impurities is predicted to differ significantly from that of most materials. Scanning tunneling microscopy (STM) and scanning tunneling spectroscopy (STS) can provide detailed information on both the spatial and energy dependence of graphene's electronic structure in the presence of a charged impurity. The design of a hybrid impurity-graphene device, fabricated using controlled deposition of impurities onto a back-gated graphene surface, has enabled several novel methods for controllably tuning graphene's electronic properties. Electrostatic gating enables control of the charge carrier density in graphene and the ability to reversibly tune the charge<sup>2</sup> and/or molecular<sup>5</sup> states of an impurity. This paper outlines the process of fabricating a gate-tunable graphene device decorated with individual Coulomb impurities for combined STM/STS studies. These studies provide valuable insights into the underlying physics, as well as signposts for designing hybrid graphene devices.

### Video Link

The video component of this article can be found at https://www.jove.com/video/52711/

### Introduction

Graphene is a two-dimensional material with a unique linear band structure, which gives rise to its exceptional electrical, optical, and mechanical properties. <sup>1,9-16</sup> Its low-energy charge carriers are described as relativistic, massless Dirac fermions <sup>15</sup>, whose behavior differs significantly from that of non-relativistic charge carriers in traditional systems. <sup>15-18</sup> Controlled deposition of a variety of impurities onto graphene provides a simple yet versatile platform for experimental studies of the response of these relativistic charge carriers to a range of perturbations. Investigations of such systems reveal that graphene impurities can shift the chemical potential<sup>6,7</sup>, alter the effective dielectric constant<sup>8</sup>, and potentially lead to electronically mediated superconductivity<sup>9</sup>. Many of these studies <sup>6-8</sup> employ electrostatic gating as a means to tuning the properties of the hybrid impurity-graphene device. Electrostatic gating can shift the electronic structure of a material with respect to its Fermi level without hysteresis. <sup>2-5</sup> Moreover, by tuning the charge<sup>2</sup> or molecular states of such impurities, electrostatic gating can reversibly modify the properties of a hybrid impurity-graphene device.

Back-gating a graphene device provides an ideal system for investigation by scanning tunneling microscopy (STM). A scanning tunneling microscope consists of a sharp metal tip held a few angstroms away from a conductive surface. By applying a bias between the tip and the surface, electrons tunnel between the two. In the most common mode, constant current mode, one can map the topography of the sample surface by raster-scanning the tip back and forth. Additionally, the local electronic structure of the sample can be studied by examining a differential conductance dI/dV spectrum, which is proportional to local density of states (LDOS). This measurement is often termed scanning tunneling spectroscopy (STS). By separately controlling the bias and back-gate voltages, the response of graphene to impurities can be studied by analyzing the behavior of these dI/dV spectra.<sup>2-5</sup>

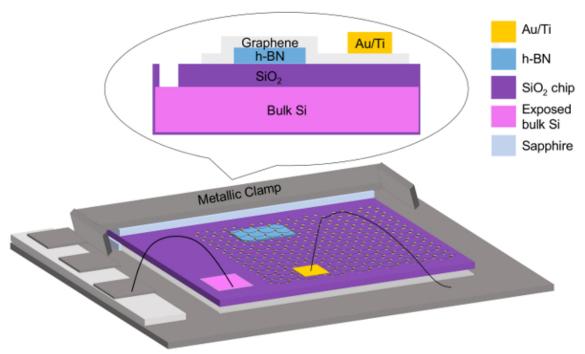

In this report, the fabrication of a back-gated graphene device decorated with Coulomb impurities (e.g., charged Ca atoms) is outlined. The device consists of elements in the following order (from top to bottom): calcium adatoms and clusters, graphene, hexagonal boron nitride (h-BN),

<sup>&</sup>lt;sup>1</sup>Department of Physics, University of California at Berkeley

<sup>&</sup>lt;sup>2</sup>Department of Chemistry, University of California at Berkeley

<sup>&</sup>lt;sup>3</sup>Department of Chemical and Biomolecular Engineering, University of California at Berkeley

<sup>&</sup>lt;sup>4</sup>National Institute for Materials Science (Japan)

<sup>&</sup>lt;sup>5</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory

<sup>&</sup>lt;sup>6</sup>Kavli Energy NanoSciences Institute, University of California at Berkeley and Lawrence Berkeley National Laboratory

silicon dioxide ( $SiO_2$ ), and bulk silicon (**Figure 1**). h-BN is an insulating thin film, which provides an atomically flat and electrically homogeneous substrate for the graphene. <sup>19-21</sup> h-BN and  $SiO_2$  act as dielectrics, and bulk Si serves as the back-gate.

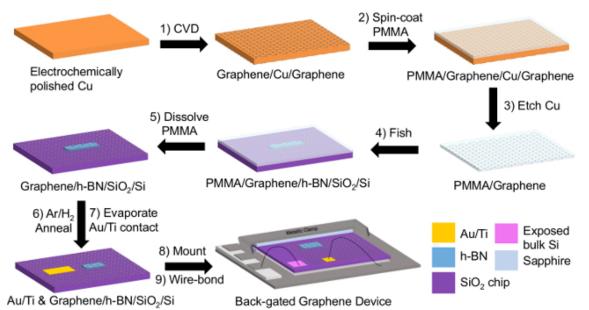

To fabricate the device, graphene is first grown on an electrochemically polished Cu foil $^{22,23}$ , which acts as a clean catalytic surface for the chemical vapor deposition  $(\text{CVD})^{22\cdot25}$  of graphene. In a CVD growth, methane  $(\text{CH}_4)$  and hydrogen  $(\text{H}_2)$  precursor gases undergo pyrolysis to form domains of graphene crystals on the Cu foil. These domains grow and eventually merge together, forming a polycrystalline graphene sheet. The resulting graphene is transferred onto the target substrate, an h-BN/SiO<sub>2</sub> chip (prepared by mechanical exfoliation  $^{19\cdot21}$  of h-BN onto an SiO<sub>2</sub>/Si(100) chip), *via* poly(methyl methacrylate) (PMMA) transfer. The PMMA transfer, the graphene on Cu is first spin-coated with a layer of PMMA. The PMMA/graphene/Cu sample then floats on an etchant solution (e.g., FeCl<sub>3</sub> (aq) $^{28}$ ), which etches away the Cu. The unreacted PMMA/graphene sample is fished with an h-BN/SiO<sub>2</sub> chip and subsequently cleaned in an organic solvent (e.g., CH<sub>2</sub>Cl<sub>2</sub>) and Ar/H<sub>2</sub> environment  $^{29,30}$  to remove the PMMA layer. The resulting graphene/h-BN/SiO<sub>2</sub>/Si sample is then wire-bonded to electrical contacts on an ultrahigh-vacuum (UHV) sample plate and annealed in an UHV chamber. Finally, the graphene device is deposited *in situ* with Coulomb impurities (e.g., charged Ca atoms) and studied by STM.

#### **Protocol**

# 1. Electrochemical Polishing of a Cu Foil<sup>22,23</sup>

Note: Electrochemical polishing exposes bare Cu surface for graphene growth by removing the protective surface coating and controls the growth seed density.

- 1. Prepare an electrochemical polishing solution by mixing 100 ml ultra-pure water, 50 ml ethanol, 50 ml phosphoric acid, 10 ml isopropanol, and 1 g urea.

- 2. Cut Cu foil into multiple 3 cm by 3 cm foils. Note: Each foil serves as either an anode or a cathode.

- 3. Set up the anode/cathode by clipping a Cu foil vertically with a holder and connecting it to the appropriate terminal of the power supply. Note: The anode (positive terminal) will be electrochemically polished for graphene growth.

- 4. Before the polishing begins, set constant voltage of 4.8 V in the power supply.

- 5. Turn on the power supply as soon as the anode and the cathode are simultaneously dipped into the electrochemical polishing solution. Separate the electrodes by about 2 cm. Check that the resulting current is between 1-2 A.

- Stop electrochemical polishing after 2 min by turning off the power supply. Take out the anode and immediately rinse it separately with ultrapure water, acetone, and isopropanol.

- 7. Blow-dry the rinsed Cu foil with N<sub>2</sub> gas and store it in a dry container.

# 2. Chemical Vapor Deposition (CVD) of Graphene on a Cu Foil<sup>22-25</sup>

- 1. Place a quartz tube in a CVD furnace and connect the tube to the rest of the gas line with KF fittings.

- 2. Place an electrochemically polished Cu foil on top of a quartz boat. Using a long rod, push the quartz boat into the quartz tube until the Cu foil is placed at the center of the CVD furnace. Enclose the system with KF fittings.

- 3. Pump down the system with a roughing pump. Purge the system with H<sub>2</sub>.

- Ramp up the temperature to 1,050 °C with 200 sccm of H<sub>2</sub>. Anneal at 1,050 °C with the same gas flow for 2 hr. Note: The temperature is measured via built-in Type K thermocouple in a tube furnace.

- 5. Cool down to 1,030 °C with the same gas flow. Grow graphene for 10 min with 40 sccm CH₄ and 10 sccm H₂.

- 6. As soon as the growth is over, open up the furnace hood to cool rapidly down toRT. Keep the same gas flow.

- 7. Once the temperature is below 100 °C, turn off the gas flow.

- 8. Turn off the pump. Vent the system with N2 gas by slowly opening the metering valve between the gas line and the N2 gas cylinder.

- 9. Take out the sample. Cut the Cu foil into pieces with desired dimensions.

- 10. Store the sample in a dry container inside a desiccator.

### 3. Mechanical Exfoliation 19-21 of h-BN onto a SiO<sub>2</sub> Chip

- 1. Clean an SiO<sub>2</sub> chip. Note: The SiO<sub>2</sub> chip consists of a roughly 285 nm thick SiO<sub>2</sub> layer on top of a bulk Si.

- 1. Cut a SiO<sub>2</sub> wafer into about 1 cm by 1 cm chips using a diamond scribe.

- 2. Rinse the SiO<sub>2</sub> chip with water and isopropanol. Keep the SiO<sub>2</sub> surface covered with water/isopropanol after each rinse.

- 3. Place the SiO<sub>2</sub> chip on the spin coater to remove liquid from its surface. Spin the chip with 3,000 rpm for 15 sec.

- 4. Check the cleanliness of the chip under an optical microscope with dark field setting. Note: Under dark field setting, solid impurities appear as bright particles.

- 2. Place a clean SiO<sub>2</sub> chip, exfoliation tape, and h-BN crystal on a clean table with an optical microscope.

- 3. Prepare two strips of tape: a parent tape and a second tape. Place both on the table with their sticky sides up. Place a h-BN crystal on the sticky side of the parent tape.

- 4. Place the sticky side of the second tape over the h-BN crystal on the parent tape (so that sticky sides of the second and parent tapes are touching). Rub over the crystal gently to remove trapped air bubbles.

- 5. Peel the second tape off to exfoliate the h-BN crystal onto the second tape. Store the parent tape for future use.

- 6. Fold the second tape onto itself, rub gently over the crystal, and peel off the tape. Repeat this process 10 times, folding the second tape so that the h-BN crystals are transferred to a fresh new region of the second tape each time.

- 7. Place a clean SiO<sub>2</sub> chip under the microscope. Stick the region of the second tape containing the h-BN crystal onto the SiO<sub>2</sub> chip. Ensure that the tape also sticks to the microscope stand for securing the chip during the upcoming exfoliation step.

- 8. Slowly peel off the tape, monitoring the process under the microscope. As the tape is nearly peeled off, use a tweezer to hold the SiO<sub>2</sub> chip in place. Note: Peeling too fast will result in less h-BN flakes on the chip.

- 9. Once the tape is peeled off, place the chip inside a CVD furnace. Anneal the chip in air at 500 °C for 2 hr.

### 4. Poly(methyl methacrylate) (PMMA)<sup>26-28</sup> Transfer of Graphene onto h-BN/SiO<sub>2</sub>

- 1. Put one drop of PMMA (A4) on the graphene/Cu/graphene foil. Spin-coat the foil with 3,000 rpm in 30 sec. Note: As FeCl<sub>3</sub> (aq) etches away the Cu layer during the upcoming etching step, the backside graphene will fall off while the PMMA/graphene layer will remain unreacted (Figure 2).

- 2. Using a FeCl<sub>3</sub> resistant spoon, let the spin-coated Cu foil float on the following solutions in this order: 1.5 min on FeCl<sub>3</sub> (aq), 5 min on ultrapure water, 1 min on FeCl<sub>3</sub> (aq), 5 min on ultra-pure water, 15 min on FeCl<sub>3</sub> (aq), 5 min on ultra-pure water, 5 min on ultra-pure water, and 30 min on ultra-pure water. Prepare each ultra-pure water bath in a separate beaker.

- 3. Fish the PMMA/graphene sample with a h-BN/SiO<sub>2</sub> chip. Place it on a hot plate at 80 °C for 10 min to remove water and at 180 °C for 15 min to relax<sup>27</sup> PMMA film.

- 4. Place the PMMA/graphene/h-BN/SiO<sub>2</sub> chip in CH<sub>2</sub>Cl<sub>2</sub> O/N to dissolve the PMMA layer.

# 5. Ar/H<sub>2</sub> Annealing<sup>29,30</sup>

- 1. Place the quartz tube on the CVD furnace and connect the tube to the rest of the gas line with KF fittings.

- 2. Place the graphene/BN/SiO<sub>2</sub> chip on a quartz boat. Using a long rod, push the quartz boat into the quartz tube until the chip is placed at the center of the CVD furnace. Enclose the system with KF fittings.

- 3. Pump down the system with a roughing pump. Purge the system with H<sub>2</sub> and Ar.

- 4. Build up the pressure to 1 atm with 100 sccm H<sub>2</sub> and 200 sccm Ar with a metering valve. Once the pressure reaches 1 atm, adjust the aperture size of the metering valve to stabilize the pressure at 1 atm.

- Ramp up the temperature to 350 °C and anneal for 5 hr with the same gas flow.

- Cool down to RT with the same gas flow.

- 7. Once the temperature is below 100 °C, turn off the gas flow. Close all valves.

- 8. Turn off the pump. Vent the system with N<sub>2</sub> gas by slowly opening the metering valve between the gas line and the N<sub>2</sub> gas cylinder.

- Take out the sample. Check the number of graphene layers and defect level with Raman spectroscopy<sup>32</sup>. Check its cleanliness/uniformity under optical microscope. Scan multiple areas that appear clean under the optical microscope with atomic force microscope (AFM) to ensure that the sample appears clean/uniform at a small length scale (<500 nm) as well.

- 10. Store it in a dry container inside a desiccator.

### 6. Assembling a Gate-tunable Graphene Device for STM Measurement<sup>2-5</sup>

- 1. Evaporate a 50  $\mu$ m by 50  $\mu$ m Au/Ti contact pad onto the Ar/H<sub>2</sub>-annealed CVD graphene/h-BN/SiO<sub>2</sub> sample.

- Tape the sample onto a stage on top of a micromanipulator.

While monitoring with optical microscope, align a stencil mask with graphene using the micromanipulator so that the Au/Ti contact will be deposited near the region of interest without covering the surface.

- 3. Transfer the sample with stencil mask to an e-beam evaporator. Evaporate 10 nm of Ti at 3 Å/sec. Cover up the Ti layer by evaporating 30-50 nm of Au at 3 Å/sec in the same evaporation session without breaking vacuum. Note: Alternatively, 1 nm of Cr is a good substitute for the 10 nm of Ti.

- Transfer the sample with stencil mask back to the micromanipulator for removing the stage.

- 2. Mount the sample onto an ultra-high-vacuum (UHV) sample plate.

- 1. Place a thin piece of sapphire on a UHV sample plate. Note: The sapphire acts as an insulating layer that prevents electrical contact between the Si and STM ground. Furthermore, sapphire is an excellent thermal conductor for the purpose of sample annealing.

- 2. Place the sample on top of the sapphire. Place another thin piece of sapphire on the sample. Make sure that the sapphire does not cover the graphene surface.

- 3. Secure the sapphire/sample/sapphire structure with a metallic clamp. Ensure that the entire structure is rigid or else it will vibrate inside a STM.

- Wire-bond the UHV sample plate terminals to appropriate contacts on the graphene device. Note: The deposited Au/Ti electrodes are wirebonded to ground while the Si bulk is wire-bonded to the gate electrode (Figure 1).

- 1. Place the mounted sample on a grounded wire-bonding stage.

- Identify locations of the Au/Ti contacts using an optical microscope.

- Turn on a wire-bonder. If the wire-bonder is pneumatic, turn on N<sub>2</sub> gas. Set the wire-bonder to make two bonds.

- 4. Using a wire-bonding arm, place the tip of the wire bonder on top of the appropriate terminal on the UHV sample plate. Move down and gently press the tip of the wire bonder onto the terminal until the wire-bonder indicates that the bonding is finished.

- Thread a wire to the Au/Ti contact on the graphene device. Move down and gently press the tip of the wire bonder onto the Au/Ti contact until the wire-bonder indicates that the bonding is finished.

- Use a diamond scribe to scratch off some SiO<sub>2</sub> on the edge of the SiO<sub>2</sub> chip to expose the Si that will be used as a back-gate. Repeat the two-bonding process for the exposed Si.

- 7. Insert the sample inside a UHV (10<sup>-10</sup> Torr) prep chamber and anneal the wire-bonded graphene device at around 300 °C. Transfer the device to a STM chamber.

Note: The graphene device should be annealed until its surface appears clean under STM (see Sec. 8 of the Protocol). The annealing time will vary depending on the initial cleanliness of the device.

### 7. STM Tip Calibration on Au(111) Surface<sup>31</sup>

- 1. Anneal/sputter an Au(111) sample on the heater stage in a UHV chamber to clean/flatten the Au surface. Anneal for 5 min at 375 °C, and sputter for 5 min with Ar<sup>+</sup> beam accelerated to 500 V. Transfer the Au(111) sample to the STM scanning stage.

- 2. Approach an Au(111) surface with a STM tip. Apply 10 V pulses on the STM tip until an Au(111) herringbone reconstruction is clearly visible.

- Calibrate the tip by adjusting the tip shape and comparing the differential conductance dI/dV spectrum to the standard Au(111) dI/dV spectrum.

- 1. Scan the Au(111) surface with 40 nm by 40 nm frame to identify a clean/flat area. If the surface has a high density of step edges, move to a new area for scanning.

- Gently crash the STM tip 0.4 to 1.0 nm into a clean region of the Au(111) surface; this controlled crashing is referred to as a "poke."

Turn off the feedback and click "Take Spectroscopy" button to take a dl/dV spectrum via lock-in onto the current response of an ac modulated voltage (6 mV and 613.7 Hz) added to the tip bias.

- Note: Once ac modulated voltage (6 mV and 613.7 Hz) is provided on the tip, the resulting tunneling current goes into the lock-in amplifier, which isolates the component of the current with the same frequency and returns dl/dV signal. By recording this signal as the sample bias is swept from -1.0 to 1.0 V, dl/dV spectrum is generated. Because this spectroscopy program is home-written, the instruction for taking the spectroscopy will vary among different programs.

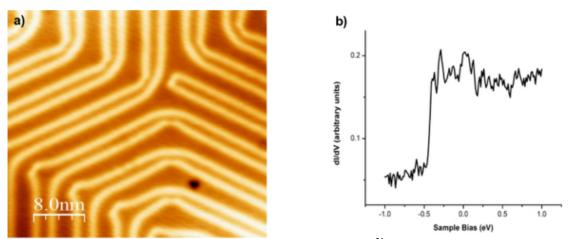

- 3. Check the obtained dl/dV curve against a standard Au(111) dl/dV spectrum (**Figure 4**). Make sure the Au(111) surface state is present in the dl/dV curve and that the spectrum is absent of any anomalous feature. If the measured dl/dV curve is not acceptable, repeat the poke in step 7.3.2 until the dl/dV curve looks like the one shown in **Figure 4**.

- 4. Once tip shape and *dl/dV* spectrum are optimized, wait 15 to 30 min; if the STM tip is unstable, *dl/dV* spectrum will change during this time interval. Retake a *dl/dV* spectrum at a different location to confirm whether the STM tip is stable or not.

- 5. Repeat the poke in step 7.3.2 if dl/dV curve has changed. Proceed to scan graphene if dl/dV curve is unchanged.

### 8. Scanning Graphene

- 1. Transfer the graphene device to a STM scanning stage.

- 2. Use a long-distance optical microscope to see the STM tip and graphene device. After laterally aligning the tip and h-BN flake of interest, approach the graphene.

- 3. Start scanning a 2 nm by 2 nm area. Slowly enlarge the scan window to 5 nm by 5 nm, 10 nm, by 10 nm, 15 nm by 15 nm, 20 nm by 20 nm, etc. If a large impurity (>100 pm in height) is encountered, withdraw the tip and move to a different area.

- 4. Take a dl/dV spectrum and compare to the standard dl/dV spectrum on graphene/h-BN substrate (see Ref. 21). If the spectrum is not comparable, recalibrate the tip on an Au(111) surface (see Sec. 7 of the Protocol).

- 5. Scan multiple areas to get a sense of how frequently large impurity (>100 pm in height) is encountered. Based on these statistics, deduce the cleanliness of the sample.

### 9. Depositing Coulomb Impurities on a Graphene Surface<sup>2-4</sup>

- 1. Obtain a Ca source. Calibrate the evaporation of Ca atoms with a residual gas analyzer (RGA) and quartz crystal microbalance (QCM) in an UHV test chamber. Note: RGA evaluates the purity of Ca deposit while QCM measures a Ca deposition rate.

- 1. Run current through the Ca source.

- 2. Increase the current until a Ca partial pressure of 10<sup>-10</sup> Torr is detected in the RGA mass spectrum. Be aware of the fact that Ca and Ar have the same mass and therefore are indistinguishable in the RGA.

- 3. Measure the Ca deposition rate (layer/sec) with the QCM.

- 1. Input the density (e.g., 1.55 g/cm<sup>3</sup> for Ca ion) of the deposit to convert frequency shift value to deposition rate.

- 2. The deposition rate monitor for the QCM reads the deposition rate in /s; convert this to layer/sec by assuming that the thickness of a monolayer is equal to the ionic diameter (e.g., 0.228 Å for Ca ion) of the deposit.

- 4. Determine the optimal current by adjusting the current until the deposition rate monitor indicates a desired deposition rate (e.g., 3.33 x 10<sup>-5</sup> layer/sec).

- Given the deposition rate (e.g., 3.33 x 10<sup>-5</sup> layer/sec) in step 9.1.3, calculate the time (sec) for depositing the desired amount (e.g., 0.01 monolayer) of Ca. In the STM, deposit Ca on a Cu(100) surface in situ with the optimal current setting from step 9.1.3. Check the Ca coverage and cleanliness of the post-deposition Cu(100) surface with STM (see step 8.5); recalibrate the current setting until the Cu(100) surface condition under STM appears as expected.

- Note: Deposition parameters are optimized on Cu(100) first to minimize the risk of contaminating the graphene device with poorly controlled deposition

- 3. Transfer the graphene device to a STM for in situ deposition at 4 K.

- 4. Deposit charged Ca atoms onto the graphene surface.

- 1. Before depositing Ca on graphene, outgass the Ca source. Slowly increase the current on the source by 0.25 A every 5-10 min until the desired current in step 9.2 is reached. Close a shutter between the graphene and Ca source to prevent outgassed contaminants from reaching the graphene.

- 2. Let the evaporation flux stabilize for 20 min before opening the shutter.

- 3. Open the shutter and deposit desirable (e.g., 0.01 monolayer) amount of Ca ions onto the graphene surface. Ensure that the graphene device has line-of-sight with the Ca source. Ensure that the STM tip is out of line-of-sight of the Ca source to prevent Ca atoms from sticking to the STM tip.

- 5. Check the Ca coverage and cleanliness of the post-deposition graphene surface with STM (see Step 8.5). Refer to Ref. 2, 3, and 4 for further protocol of the study of Coulomb impurities on graphene.

#### Representative Results

**Figure 1** illustrates a schematic of a back-gated graphene device. Wire-bonding Au/Ti contact to an UHV sample plate grounds graphene electrically, while wire-bonding Si bulk to an electrode that connects to an external circuit back-gates the device. By back-gating a device, a charge state of a Coulomb impurity at a given sample bias (which is controlled by the STM tip) can be tuned to a different charge state.<sup>2-4</sup>

**Figure 2** outlines the steps for fabricating a gate-tunable graphene device. A Cu foil is first electrochemically polished to remove its protective surface coating and modify its growth seed density. <sup>23,24</sup> After electrochemical polishing, the Cu foil should appear shinier under the naked eye than before as its surface should have become smoother. The electrochemically polished Cu foil then acts as a catalytic substrate for CVD growth of graphene. Graphene is then transferred onto an h-BN/SiO<sub>2</sub> substrate *via* PMMA transfer. The resulting sample is cleaned in an Ar/H<sub>2</sub> atmosphere and characterized (**Figure 3**). Subsequently, it is assembled into a back-gated device.

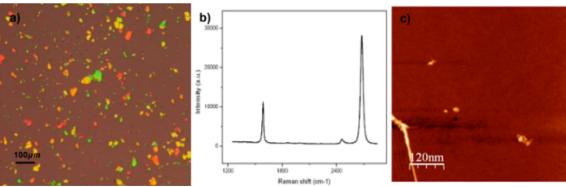

Before the sample is assembled into a back-gated device, the graphene surface is characterized by an optical microscope (**Figure 3A**), Raman spectroscopy (**Figure 3B**), and AFM (**Figure 3C**). With an optical microscope image, it is easy to examine the cleanliness, continuity, and the number of graphene layers throughout the entire sample. With a Raman spectrum, the number of graphene layers and defect level can be evaluated by examining the  $I_{G}$ : $I_{2D}$  peak intensity ratio and D peak intensity, respectively. With an AFM image, various features — cleanliness, uniformity, surface roughness, *etc.* — of the sample can be reliably evaluated at a small length scale (<500 nm). A good sample should appear clean, continuous, uniform, and monolayered under both optical microscope and AFM images. Moreover, a good sample should exhibit a minimal D peak intensity (a sign of minimal defect) and less than 1:2 ratio of  $I_{G}$ : $I_{2D}$  peak intensity ratio (a sign of monolayer) under Raman spectroscopy. <sup>32</sup>

Before the device can be characterized under a STM, a STM tip must be calibrated on an Au(111) surface to decouple the STM tip states from the sample's surface states as much as possible. Without the tip calibration, the differential conductance dI/dV spectrum will appear convoluted due to a strong coupling between the tip states and the sample's surface states: in other words, STM data taken from an uncalibrated tip may not represent the real property of the sample. To calibrate the tip, the STM tip is repetitively pulsed/poked into an Au(111) surface until a high resolution image of herringbone reconstruction (**Figure 4A**) can be obtained and a dI/dV spectrum appears comparable to the standard Au(111) dI/dV spectrum (**Figure 4B**). The dI/dV spectrum should exhibit a sharp step at  $V_{\text{sample}} \approx -0.5$  V, which represents the onset of the Au(111) surface state. Moreover, the dI/dV spectrum should exhibit no anomalous peaks and dips, which may appear as artifacts when performing dI/dV measurements on graphene.

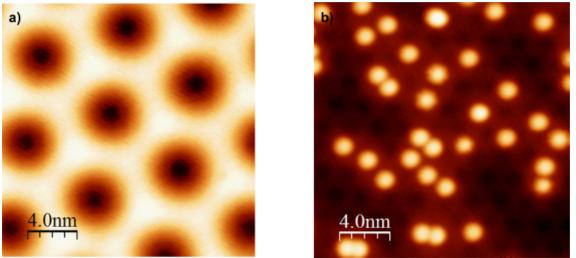

After the tip calibration, the sample surface is examined with STM. **Figure 5A** shows a Moiré pattern for graphene/h-BN, which arises from a mismatch in the lattice constants of graphene and h-BN. The wavelength of a Moiré pattern depends on the angle of rotation between the graphene and underlying h-BN lattices: smaller the twist angle, greater the wavelength. Appearance of Moiré pattern confirms the presence of clean graphene on an h-BN substrate. Once the sample surface is examined, Ca ions are deposited onto graphene, whose topography is shown in **Figure 5B**. A Moiré pattern appears in the background of the image. Once charged Ca atoms are successfully deposited, STM tip can construct artificial nuclei consisting of multiple charged Ca dimers by pushing each dimer into small clusters. STM study results for charged Co and Ca adatoms are shown in Ref. 2 & 3 and Ref. 4, respectively.

**Figure 1. Schematic of a gate-tunable graphene device.** Graphene is grounded to the sample plate while Si layer connects to a gate electrode through wire-bonding. <sup>2-5</sup> Please click here to view a larger version of this figure.

Figure 2. Process schematics of gate-tunable graphene device fabrication. The steps of fabricating a gate-tunable graphene device include: 1) CVD graphene growth on an electrochemically polished Cu foil, 2) – 5) PMMA transfer of graphene onto a h-BN/SiO<sub>2</sub> chip, 6) Ar/H<sub>2</sub> annealing, 7) evaporation of Au/Ti contact, 8) mounting onto an UHV sample plate, and 9) wire-bonding. Please click here to view a larger version of this figure.

**Figure 3. Pre-STM characterization of a graphene/h-BN/SiO<sub>2</sub> heterostructure. (A)** Optical microscope image of graphene/h-BN/SiO<sub>2</sub> heterostructure. **(B)** Raman spectrum of graphene/SiO<sub>2</sub> region. Raman spectrum of graphene is characterized by D (~1,350 cm<sup>-1</sup>), G (~1,580 cm<sup>-1</sup>), and 2D (~2,690 cm<sup>-1</sup>) peaks.<sup>32</sup> **(C)** Atomic force microscope (AFM) image of graphene/h-BN/SiO<sub>2</sub> region. This image is a height map taken with tapping mode AFM. Please click here to view a larger version of this figure.

Figure 4. STM characterization of Au(111) surface for STM tip calibration.<sup>31</sup> (A) Topography of Au(111) surface. (B) Standard dl/dV spectrum of Au(111) surface. Please click here to view a larger version of this figure.

Figure 5. STM Topography of Coulomb impurities on graphene. (A) Moiré pattern for graphene/h-BN.<sup>20,21</sup> (B) Ca adatoms on graphene. Please click here to view a larger version of this figure.

#### **Discussion**

For STM characterization, critical goals of the graphene device fabrication include: 1) growing monolayer graphene with a minimal number of defects, 2) obtaining a large, clean, uniform, and continuous graphene surface, 3) assembling a graphene device with high resistance between the graphene and the gate (*i.e.*, no "gate leakage"), and 4) depositing individual Coulomb impurities.

The first goal is governed by the CVD process, during which graphene grows on a Cu foil. Although there are multiple substrate candidates (e.g., Ni, Ru, Ir, Pt, Co, Pd, etc.), Cu is well known to produce monolayer graphene most selectively due to its extremely low carbon solubility. Nevertheless, selectively growing monolayer graphene can still be difficult and inconsistent due to a wide range of factors. Although electrochemical polishing certainly provides a better substrate condition for graphene growth, our AFM characterizations have shown that the Cu surface remains non-uniform and rough on the microscopic level. Moreover, the level of contamination from chemical residue may vary from foil to foil. Annealing parameters are essential for consistently providing a clean and uniform Cu surface during growth. Annealing the Cu at a high temperature (1,050 °C) near its melting point (1,085 °C) with a high flow of hydrogen (~200 sccm) seems to provide a consistently clean and uniform Cu surface with large Cu domains. The growth temperature, pressure regime, and CH<sub>4</sub>:H<sub>2</sub> flow rate ratio can then be systematically optimized until monolayer graphene with a minimal number of defects is obtained.

The second goal — obtaining a large, clean, uniform, and continuous graphene surface — is governed by the PMMA transfer and Ar/H<sub>2</sub> annealing. Although there are a number of different graphene transfer methods (*e.g.*, dry PMMA/PDMS transfer<sup>27</sup>, wet PDMS transfer<sup>24</sup>, *etc.*), PMMA transfer with FeCl<sub>3</sub> (aq) etchant solution<sup>28</sup> has consistently yielded the most continuous/uniform graphene surfaces. However, this method leaves a high density of chemical residue on the graphene surface. To resolve this issue, the spin-coating rate and time were first optimized to make the PMMA layer as uniform as possible. Additionally, multiple cleaning steps with ultra-pure water baths were introduced to remove chemical residue from the graphene's back surface before fishing it out with an h-BN/SiO<sub>2</sub> chip. From these efforts, relatively clean samples, as seen by an optical microscope, have been transferred consistently. No variation in the PMMA transfer method, however, can completely clean up the graphene surface as it always leaves a thin layer of PMMA. To obtain an atomically clean surface (STM studies require clean regions >100 nm<sup>2</sup>), a series of annealing procedures must be performed. Ar/H<sub>2</sub> annealing can effectively remove a majority of the PMMA layer. After Ar/H<sub>2</sub> annealing,<sup>29</sup> the graphene surface appears to be clean under inspection by ambient AFM (**Figure 3**). Yet, a thin PMMA layer undetectable by ambient AFM still covers the graphene surface, which requires further *in situ* UHV annealing to remove. It is important to keep in mind that post-transfer annealing can only clean a relatively residue-free surface only; a sample's ultimate cleanliness depends mainly on the transfer.

The third goal — assembling a graphene device without any gate leakage — is governed by post-Ar/H<sub>2</sub> annealing steps. When mounting the device on a sample plate, it is critical to electrically disconnect the device from the rest of the sample plate with sapphire flakes; the only electrical contact between the sample plate and the device should be the wire-bonds. Wire-bonding introduces the risk of breaking the device if excessive power is supplied as any form of fracture in the SiO<sub>2</sub> layer (regardless of how small) may lead to gate leakage. Wire-bonding parameters must thus be optimized ahead of time. Because gate leakage may occur not only in the device but also throughout the STM chamber, a large amount of time and resources may be wasted to identify and fix the leakage source. It is important to minimize the risk of gate leakage while assembling a graphene device.

The fourth goal — depositing individual Coulomb impurities — is governed by the calibration steps prior to the deposition. It is imperative to optimize the deposition parameters in the UHV test chamber (and additionally on the Cu(100) surface *in situ*) for a controlled deposition. Purity of the deposition needs to be carefully evaluated with an RGA because random impurities will not only skew the deposition rate measured by QCM but also result in unwanted doping. If the device were irreversibly doped by an unknown impurity, the graphene's response to Coulomb impurities might be undesirably altered.

In addition to these challenges, an STM study may be limited in several ways. In a differential conductance measurement, it is impossible to completely decouple the tip electronic states from the sample states. Even with a well-calibrated tip, it may be challenging to determine the origin of a spectroscopic feature. Moreover, information gained from measurements carried out in UHV (10<sup>-10</sup> Torr) and a T = 4 K may not be relevant to devices operated in less ideal conditions.

That being said, STM has many advantages over other techniques. It has not only a high energy resolution (few meV) but also a high spatial resolution (~10 pm). For comparison, ARPES has a relatively lower spatial resolution (sub-micron), but a comparable energy resolution (few meV). STM can also be used to manipulate the position of individual atoms on a device to create novel charge configurations. For example, Yang *et al.* created artificial nuclei of charged Ca dimers on a back-gated graphene device with an STM tip and characterized an atomic collapse state on the graphene surface. With these advantages in mind, STM is one of the most powerful and reliable techniques for characterizing the spatially dependent response of graphene to various perturbations in a well-controlled environment.

STM studies of gate-tunable graphene devices deposited with Coulomb impurities are valuable not only for testing fundamental theories but also for understanding hybrid graphene device applications. They can experimentally verify fundamental predictions about the behavior of massless Dirac fermions in novel systems, which exhibit significantly different behavior compared to charge carriers in conventional systems. Furthermore, such studies can reveal some of graphene's most unexpected characteristics<sup>4</sup>, which leads to a deeper understanding of charge carriers in relativistic regimes. New insight into the physical laws that govern graphene systems will be highly beneficial for precision tuning of the properties of hybrid graphene devices.<sup>25</sup>

#### **Disclosures**

Authors have nothing to disclose.

#### **Acknowledgements**

Our research was supported by the Director, Office of Science, Office of Basic Energy Sciences of the U.S. Department of Energy sp2 Program under contract no. DE-AC02-05CH11231 (STM instrumentation development and device integration); the Office of Naval Research (device characterization), and NSF award no. CMMI-1235361 (dI/dV imaging). STM data were analyzed and rendered using WSxM software. 33 D. W. and A.J.B. were supported by the Department of Defense (DoD) through the National Defense Science & Engineering Graduate Fellowship (NDSEG) Program, 32 CFR 168a.

### References

- 1. Novoselov, K. S., et al. Electric field effect in atomically thin carbon films. Science. 306, (5696), 666-669 (2004).

- 2. Brar, V. W., et al. Gate-controlled ionization and screening of cobalt adatoms on a graphene surface. Nat. Phys. 7, (1), 43-47 (2011).

- 3. Wang, Y., et al. Mapping Dirac quasiparticles near a single Coulomb impurity on graphene. Nat. Phys. 8, (9), 653-657 (2012).

- 4. Wang, Y., et al. Observing atomic collapse resonances in artificial nuclei on graphene. Science. 340, (6133), 734-737 (2013).

- 5. Riss, A., et al. Imaging and tuning molecular levels at the surface of a gated graphene device. ACS Nano. 8, (6), 5395-5401 (2014).

- 6. Chen, J. H., Jang, C., Adam, S., Fuhrer, M. S., Williams, E. D., Ishigami, M. Charged-impurity scattering in graphene. *Nat. Phys.* 4, (5), 377-381 (2008).

- 7. Pi, K., et al. Electronic doping and scattering by transition metals on graphene. Phys. Rev. B. 80, (7), 075406 (2009).

- 8. Jang, C., et al. Tuning the effective fine structure constant in graphene: Opposing effects of dielectric screening on short- and long-range potential scattering. Phys. Rev. Lett. 101, (14), 146805 (2008).

- 9. McChesney, J. L., et al. Extended van Hove singularity and superconducting instability in doped graphene. Phys. Rev. Lett. 104, (13), 136803 (2010).

- 10. Geim, A. K., Novoselov, K. S. The rise of graphene. Nat. Mater. 6, (3), 183-191 (2007).

- 11. Wang, F., et al. Gate-variable optical transitions in graphene. Science. 320, (5873), 206-209 (2008).

- 12. Lee, C., Wei, X. D., Kysar, J. W., Hone, J. Measurement of the elastic properties and intrinsic strength of monolayer graphene. *Science*. **321**, (5887), 385-388 (2008).

- 13. Zhang, Y., et al. Giant phonon-induced conductance in scanning tunneling spectroscopy of gate-tunable graphene. Nat. Phys. 4, (8), 627-630 (2008).

- 14. Zhang, Y., Tan, Y. W., Stormer, H. L., Kim, P. Experimental observation of the quantum Hall effect and Berry's phase in graphene. *Nature*. **438**, (7065), 201-204 (2005).

- 15. Novoselov, K. S., et al. Two-dimensional gas of massless Dirac fermions in graphene. Nature. 438, (7065), 197-200 (2005).

- 16. Biswas, R. R., Sachdev, S., Son, D. T. Coulomb impurity in graphene. Phys. Rev. B. 76, (20), 205122 (2007).

- 17. Novikov, D. S. Elastic scattering theory and transport in graphene. Phys. Rev. B. 76, (24), 245435 (2007).

- 18. Pereira, V. M., Nilsson, J., Castro Neto, A. H. Coulomb impurity problem in graphene. Phys. Rev. Lett. 99, (16), 166802 (2007).

- 19. Dean, C. R., et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, (10), 722-726 (2010).

- 20. Xue, J., et al. Scanning tunnelling microscopy and spectroscopy of ultra-flat graphene on hexagonal boron nitride. Nat. Mater. 10, (4), 282-285 (2011).

- 21. Decker, R., et al. Local electronic properties of graphene on a BN substrate via scanning tunneling microscopy. Nano Lett. 11, (6), 2291-2295 (2011).

- 22. Yan, Z., et al. Toward the synthesis of wafer-scale single-crystal graphene on copper foils. ACS Nano. 6, (10), 9110-9117 (2012).

- 23. Zhang, B., et al. Low-temperature chemical vapor deposition growth of graphene from toluene on electropolished copper foils. ACS Nano. 6, (3), 2471-2476 (2012).

- 24. Li, X., et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science. 324, (5932), 1312-1314 (2009).

- 25. Zhang, Y., Zhang, L., Zhou, C. Review of chemical vapor deposition of graphene and related applications. *Acc. Chem. Res.* **46**, (10), 2329-2339 (2013).

- 26. Reina, A., et al. Transferring and identification of single-and few-layer graphene on arbitrary substrates. J. Phys. Chem. C. 112, (46), 17741-17744 (2008).

- 27. Suk, J. W., et al. Transfer of CVD-grown monolayer graphene onto arbitrary subsrates. ACS Nano. 5, (9), 6916-6924 (2011).

- 28. Regan, W., et al. A direct transfer of layer-area graphene. Appl. Phys. Lett. 96, (11), 113102 (2010).

- 29. Ishigami, M., Chen, J. H., Cullen, W. G., Fuhrer, M. S., Williams, E. D. Atomic structure of graphene on SiO2. *Nano Lett.* 7, (6), 1643-1648 (2007).

- 30. Dan, Y., Lu, Y., Kybert, N. J., Luo, Z., Johnson, A. T. C. Intrinsic response of graphene vapor sensors. Nano Lett. 9, (4), 1472-1475 (2009).

- 31. Chen, W., Madhavan, V., Jamneala, T., Crommie, M. F. Scanning tunneling microscopy observation of an electronic superlattice at the surface of clean gold. *Phys. Rev. Lett.* **80**, (7), 1469-1472 (1998).

- 32. Saito, R., Hofmann, M., Dresselhaus, G., Jorio, A., Dresselhaus, M. S. Raman spectroscopy of graphene and carbon nanotubes. *Adv. Phys.* **60**, (3), 413-550 (2011).

- 33. Horcas, I., Fernandez, R., Gomez-Rodriguez, J. M., Colchero, J., Gomez-Herrero, J., Baro, A. M. WSXM: A software for scanning probe microscopy and a tool for nanotechnology. *Rev. Sci. Instrum.* **78**, (1), 013705 (2007).